1�� �W(xu��)��(x��)��QUARTUSIIܛ����ģ�K��̖�ļ��������c�{(di��o)�á�

2�� ����ģ�K��̖�cģ�K��̖֮�g���B��Ҏ(gu��)�t�c������

3�� ���Տ��O(sh��)Ӌ(j��)�ļ���ģ�K��̖�Ą�(chu��ng)���^�̡�

���� ��(sh��)�(y��n)ԭ��

�ڌӴλ����O(sh��)Ӌ(j��)�ļ��У���(j��ng)����Ҫ���ѽ�(j��ng)�O(sh��)Ӌ(j��)�õĹ����ļ�����һ��(g��)ģ�K��̖�ļ������Լ��Ĺ���ģ�K��̖��플��{(di��o)�ã�ԓ��̖����D���O(sh��)Ӌ(j��)�ļ��е��κ������깦�ܷ�̖һ�ӿɱ��ߌ��O(sh��)Ӌ(j��)�؏�(f��)�{(di��o)�á�����(sh��)�(y��n)�Č�(sh��)�(y��n)ԭ�����nj�ǰ���O(sh��)Ӌ(j��)�Č�(sh��)�(y��n)�����ġ���ͨ�^QUARTUSIIܛ���ϲ���һ��(g��)�O(sh��)Ӌ(j��)�ļ�����(sh��)�F(xi��n)��(sh��)�(y��n)�����ġ����е����й��ܡ�

���� ��(sh��)�(y��n)��(n��i)��

����(sh��)�(y��n)Ҫ����ɵ��΄�(w��)�c��(sh��)�(y��n)�����ġ���Č�(sh��)�(y��n)��(n��i)�ݻ���һ�¡��ڌ�(sh��)�(y��n)�У��r(sh��)���̖�xȡ1464HZ���锵(sh��)�a�ܵĒ���r(sh��)犣��܄�(d��ng)�_�P(gu��n)ݔ��һ��(g��)�A(y��)�õİ�λ��(sh��)��(j��)����(j��ng)�^��(sh��)�ط��l�·����(sh��)�(y��n)�壩���l��õ�һ��(g��)�^�͵��l������ӷ�Ӌ(j��)��(sh��)������(sh��)�(y��n)�����ĕr(sh��)��l���M(j��n)��Ӌ(j��)��(sh��)���ļӷ��\(y��n)�㡣�õ���ֵ�o��(sh��)�a�@ʾ�g�a�·����(sh��)�(y��n)�ģ��ڔ�(sh��)�a�����@ʾ������

�ġ� ��(sh��)�(y��n)���E

1�� ���_QUARTUSIIܛ�����½�һ��(g��)���̡�

2�� ����ǰ�����Č�(sh��)�(y��n)�����ġ����Դ������a��(f��)�Ƶ���(d��ng)ǰ����Ŀ��±���������

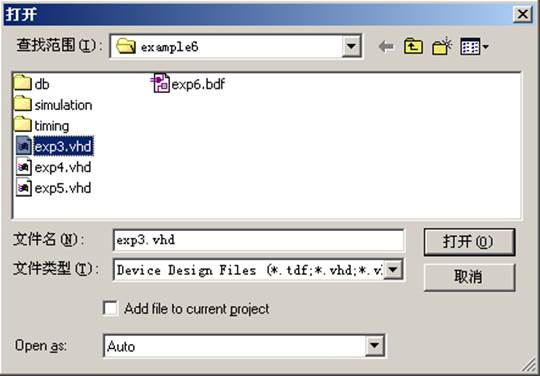

3�� �x��File>Open�����D4-6-1��ʾ�����_��(f��)�Ƶ���(d��ng)ǰ����Ŀ��º�����һ��(g��)Դ������a����EXP3.VHD����

�D4-6-1 ���_һ��(g��)�O(sh��)Ӌ(j��)�ļ�

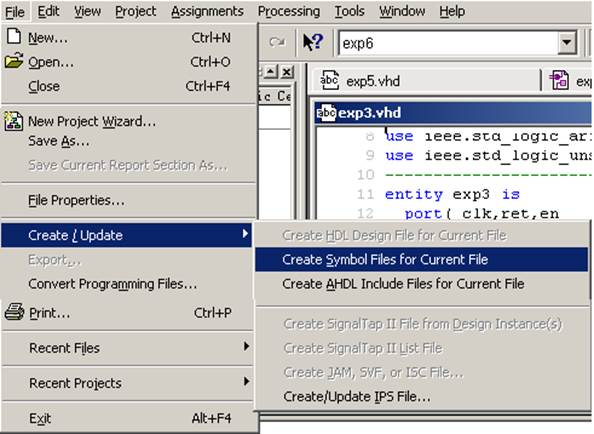

4�� ��File�ˆ����x��Create/Update�(xi��ng)���M(j��n)���x��Create Symbol for Current File���c(di��n)���_�����o�����Ʉ�(chu��ng)��һ��(g��)���턂�Ŵ��_���O(sh��)Ӌ(j��)�ļ����ܵķ�̖��.bsf������D4-6-2��ʾ�����ԓ�ļ�����(y��ng)�ķ�̖�ļ��ѽ�(j��ng)��(chu��ng)���^���t��(zh��)��ԓ�����r(sh��)��(hu��)������ʾ��Ϣ��ԃ���Ƿ�Ҫ���w�F(xi��n)��ķ�̖�ļ����Ñ����Ը���(j��)�Լ�����Ը�M(j��n)���x��

�D4-6-2 �ĬF(xi��n)���ļ���(chu��ng)��ģ�K��̖�ļ�

5�� ��ͬ�ӵķ����������O(sh��)Ӌ(j��)�ļ���EXP4.VHD��EXP5.VHD���M(j��n)��ģ�K��̖�ļ��Ą�(chu��ng)����

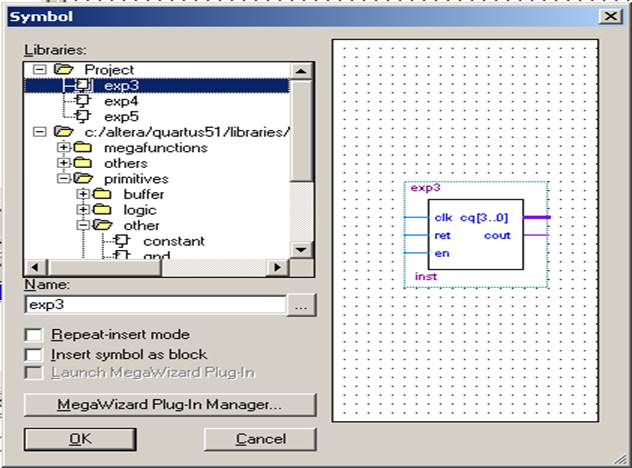

6�� ģ�K��̖�ļ���(chu��ng)����ɺ����½�һ��(g��)�D�ξ��ļ������_�D�ξ�����Ԓ���ڈD�ξ������ڵĹ����^(q��)�p�����(bi��o)�����I�����c(di��n)��D�еķ�̖���߰��o�����x��ˆ�Edit>Insert Symbol…���t������D4-6-3��ʾ��Symbol��Ԓ��

�D4-6-3 Symbol��Ԓ��

7�� ��Symbol��Ԓ�D6-3���е�Project�(xi��ng)��(hu��)���F(xi��n)ǰ�愓(chu��ng)����ģ�K��̖�ļ���EXP3��EXP4��EXP5�����҂��F(xi��n)�ھͿ��������{(di��o)���@Щ����ģ�K��̖�ļ���

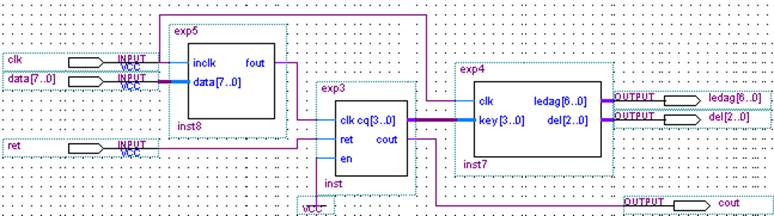

8�� �xȡ�@Щģ�K��̖�ļ����õ������^(q��)���{(di��o)����Ҫ��ģ�K��̖�Ժ��M(j��n)�з�̖֮�g���B�����Լ�����ݔ�롢ݔ�����p�����_����Ҫ�f�����ǣ����@��(g��)��(sh��)�(y��n)�У���?y��n)�ݔ��Ĕ?sh��)��(j��)ռ����ʮ��λ�ē܄�(d��ng)�_�P(gu��n)����������ͬ��ʹ�ܶ˵���̖EN�҂�������һ��(g��)VCC��̖��ʹʹ�ܶ���̖EN��Ч�������O(sh��)Ӌ(j��)��ɺ���·��D4-6-4��ʾ��

�D4-6-4 �O(sh��)Ӌ(j��)�D�η�̖�ļ�

9�� ���Լ������ĈD�η�̖ݔ���ļ������M(j��n)�б��棬Ȼ���g�����棬��������e(cu��)�`�M(j��n)���ġ�

10�� ���g����o�`����(j��)�Ñ��Լ���Ҫ���M(j��n)�й��_���䡣������ɺ����M(j��n)��ȫ���gһ�Σ���ʹ���_������Ч��

������{(di��o)�õı����ṩ��VHDL���a���t��(sh��)�(y��n)�B�����£�

CLK��FPGA�r(sh��)���̖���Ӕ�(sh��)�֕r(sh��)�CLOCK3�������@�M�r(sh��)��O(sh��)��1464HZ��

DATA[7..0]�����l��(sh��)��(j��)ݔ����̖���քe�ӓ܄�(d��ng)�_�P(gu��n)��K8-K1��

COUT��Ӌ(j��)��(sh��)�M(j��n)λݔ����̖����һ��(g��)LED��D1��

RET��Ӌ(j��)��(sh��)��(f��)λ��̖���Ӻ��İ�RST��(f��)λ���I��

LEDAG[6..0]����(sh��)�a���@ʾ��̖���Ӕ�(sh��)�a�ܵ�G��F��E��D��C��B��A��

SEL[2..0]����(sh��)�a�ܵ�λ�x��̖���Ӕ�(sh��)�a�ܵ�SEL2��SEL1��SEL0��

11�� ����(j��)��(sh��)�(y��n)��(n��i)���Ì�(sh��)�(y��n)��(d��o)����������_�����FPGA���_�c����(y��ng)��ģ�K�B��������

12�� �����d��|ͨ�^JTAG�ڌ�����(y��ng)��sof�ļ����d��FPGA�С��^�쌍(sh��)�(y��n)�Y(ji��)���Ƿ��c�Լ��ľ���˼��һ�¡�

�塢 ��(sh��)�(y��n)�F(xi��n)���c�Y(ji��)��

���O(sh��)Ӌ(j��)�ą���ʾ����������(d��ng)�O(sh��)Ӌ(j��)�ļ����d��Ŀ��(bi��o)�����_�J(r��n)��̖�B�Ӿ������_�B�ӣ��܄�(d��ng)��λ�܄�(d��ng)�_�P(gu��n)��ʹ���һ��(g��)��(sh��)ֵ���t��λ��(sh��)�a�ܰ�һ���������_ʼ�@ʾ“0-F”����(d��ng)��(sh��)�a���@ʾA-F�r(sh��)LED��LED1�_ʼ���c(di��n)�����@ʾ������(sh��)ֵ�r(sh��)Ϩ�硣�����İ��(f��)λ�I�@ʾ�Ĕ�(sh��)ֵ�֏�0�_ʼ���܄�(d��ng)��λ�܄�(d��ng)�_�P(gu��n)������������(sh��)��(j��)����(sh��)�a�ܵ��@ʾ���ʕ�(hu��)�l(f��)����׃��

���� ��(sh��)�(y��n)��(b��o)��

1�� �����沨�Σ������f����

2�� �Լ��O(sh��)Ӌ(j��)�ļ���Ȼ��ͨ�^�O(sh��)Ӌ(j��)�ļ���ģ�K��̖�ļ����D(zhu��n)�Q���O(sh��)Ӌ(j��)�Լ����·���ڌ�(sh��)�(y��n)ϵ�y(t��ng)���(y��n)�C���M(j��n)һ�������@�N������

3�� ������ܛ����ͨ�^�����������O(sh��)Ӌ(j��)�ļ���ģ�K��̖�ļ����D(zhu��n)�Q�^�̡�