���(y��) > ��I(y��)���� > ��Ʒ���] > Ӌ(j��)��C(j��)�O(sh��)Ӌ(j��)�C�ϼ���ԇ�(y��n)�䣬Ӌ(j��)��C(j��)�O(sh��)Ӌ(j��)��(sh��)�(y��n)��

Ӌ(j��)��C(j��)�O(sh��)Ӌ(j��)�C�ϼ���ԇ�(y��n)�䣬Ӌ(j��)��C(j��)�O(sh��)Ӌ(j��)��(sh��)�(y��n)��

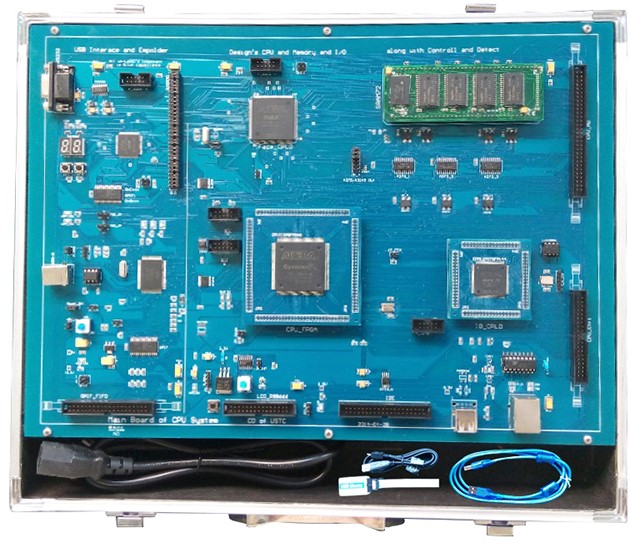

2024-05-27 06:46Ӌ(j��)��C(j��)�O(sh��)Ӌ(j��)�C�ϼ���ԇ�(y��n)����һ�N����Ӌ(j��)��C(j��)�O(sh��)Ӌ(j��)�;C�ϼ�����Ӗ(x��n)�Č�(sh��)�(y��n)�O(sh��)�䡣�@�Nԇ�(y��n)�伯����Ӌ(j��)��C(j��)Ӳ����ܛ���Ķ���(g��)���棬ʹ�Ñ��܉��ڿ����_(t��i)���M(j��n)�Ќ�(sh��)�H�IJ����͌�(sh��)�(y��n)���Ķ����Ӌ(j��)��C(j��)�O(sh��)Ӌ(j��)�;S�o(h��)�ļ��ܡ�

����1. Ӌ(j��)��C(j��)Ӳ��ƽ�_(t��i)������̎��������(n��i)�桢Ӳ�P���@�����W(w��ng)���Ⱥ��ĽM�������ژ�(g��u)���͜y(c��)ԇӋ(j��)��C(j��)ϵ�y(t��ng)��

����2. �Դϵ�y(t��ng)���ṩ��(w��n)�����Դ����(y��ng)���Еr(sh��)߀�����Դ�O(ji��n)�غͱ��o(h��)���ܡ�

����3. ݔ��/ݔ���ӿڣ���USB�����ڡ����ڡ���̫�W(w��ng)�ӿڵȣ������B���ⲿ�O(sh��)��;W(w��ng)�j(lu��)��

����4. �@ʾ�����I�P�����ڲ����ͱO(ji��n)��Ӌ(j��)��C(j��)ϵ�y(t��ng)���\(y��n)�Р�B(t��i)��

����5. ��(sh��)�(y��n)ָ��(d��o)����ܛ�������ܰ�����(sh��)�(y��n)�փ�(c��)���̌W(xu��)ܛ����̓�M��(sh��)�(y��n)�ҵ��YԴ�������Ñ�W(xu��)��(x��)�͌�(sh��)�`��

����Ӌ(j��)��C(j��)�O(sh��)Ӌ(j��)�C�ϼ���ԇ�(y��n)����Ӌ(j��)��C(j��)�ƌW(xu��)�ͼ��g(sh��)�������Ϣ���̵����P(gu��n)���I(y��)�Ľ̌W(xu��)����Ӗ(x��n)�зdz����á�ͨ�^(gu��)ʹ���@�N�O(sh��)�䣬�W(xu��)�������ڌ�(sh��)�`�ЌW(xu��)��(x��)Ӌ(j��)��C(j��)Ӳ����ܛ�����O(sh��)Ӌ(j��)������S�o(h��)�ȼ��ܣ��錢��(l��i)�Ĺ����ṩ���F�Č�(sh��)�`��(j��ng)�(y��n)��

Ӌ(j��)��C(j��)�O(sh��)Ӌ(j��)�C�ϼ���ԇ�(y��n)��

��

һ����(sh��)�(y��n)ƽ�_(t��i)�ܘ�(g��u)�c���c(di��n)

1����ȫ����FPGA/CPLD��ģ�K�ܘ�(g��u)���Y(ji��)��(g��u)֧��USB��GPIF���ق��ͣ��M�����£�

1��USB�O(sh��)���_(k��i)�l(f��)�c�ӿ�ģ�K������USB��������CY7C68013(��8051��(n��i)��)������EEPROM 24LC01B ��SRAM HY62WT081E��EPM3064ATC100����(sh��)��(j��)�����_(k��i)�P(gu��n) SN74CB3Q3245���i���� 74VHC373������USB�ӿڡ�

2��ƽ�_(t��i)�ӿڿ�����CPLDģ�K������EPM3512AQC208��оƬ�����l��DS1080L��JTAG���d�ӿڵȡ�

3��CPU��IP Core��FPGAģ�K��������������EP1C12Q240C8������оƬEPCS4��JTAG���d�ӿڵȡ�

4������ģ�K4MB SRAM����8Ƭ512K SRAM 62V8400A �M�ɣ�1MB Flash��BIOS��TOS����AM29LA800BT�M�ɡ�

5������ӿ��_(k��i)�l(f��)��CPLDģ�K����EPM1270T144C4��JTAG���d�ӿڵȡ�

6��CPU-BUS�U(ku��)��ģ�K����USB�p������MAX3346E��SRAM HY62WT081E

7����̫�W(w��ng)�ӿ�ģ�K����6PT8515������(q��)��(d��ng)��DS90LV011AH�Ͳ�ֽ�����DS90LV012AH��

8������ͨ�Žӿڣ���MAX232�ƽ�D(zhu��n)�Q����RS232-9�ӿڡ�

9��GPIF�ӿڣ���SRAM HY62WT081E��IDC-40�ӿڡ�

10�����O(sh��)Ӌ(j��)CPU�ⲿ�ӿڣ���TFT-LCD�@ʾ�ӿڡ�IDEӲ�P�ӿڡ�LAN�ӿڵȡ�

2���Y(ji��)��(g��u)�`����ڔU(ku��)�䣬�m�˸��N��ͬ�Y(ji��)��(g��u)CPU��Ŀ��(bi��o)�O(sh��)Ӌ(j��)

1����ȫ����FPGA/CPLD�ı���ʹ��Y(ji��)��(g��u)�`��

2������CPU/IP Core��FPGA��30�f(w��n)�T��������ӿڵ�CPLDʹ�ñ����D(zhu��n)�壬������Q�;S�o(h��)��

3����CPU��FPGA�O(sh��)Ӌ(j��)���ஔ(d��ng)?sh��)Ă�����?h��o)�������^�����_�B�ӡ��ṩ플��{(di��o)��Ŀ��(bi��o)��Ԕ�M����ģ������_�����ļ���

4���ӿڿ�����CPLD���f(w��n)�T��ģ�K߉�����_(k��i)�ţ����ķ��㡢�f(shu��)��Ԕ�M��

3�����ƺ�(ji��n)�Σ��������㣬���ܻ��Ŀ��ƺ͙z�y(c��)����

1��������λ���C(j��)�ı�ϵ�y(t��ng)�{(di��o)ԇdebug��WIN2K/XP��ܛ������(du��)CPU����M�ɵČ�(sh��)�(y��n)Ӌ(j��)��C(j��)�����І���ͣ��������d�cУ�(y��n)��

2���چβ�����ָ�����c(di��n)�\(y��n)�Еr(sh��)����CPU�ĸ�ۙ����߉����£�debug���Ԅ�(d��ng)��ۙ�����@ʾCPU��(n��i)���Ĵ�������������B(t��i)����Ϣ���ɼ��r(sh��)�l(f��)�F(xi��n)�e(cu��)�`���Ñ�����CPU�ĸ�ۙ����߉��Լ��x����Ҫ������Ϣ��

3��Ŀ��(bi��o)CPU����ʹ��PC�C(j��)�ĸ��N�ⲿ�O(sh��)�䣬���B�m(x��)�\(y��n)�Еr(sh��)��ͨ�^(gu��)�p�C(j��)�����C(j��)�cĿ��(bi��o)CPU��ͨӍ���Д�IO��ʽ����ݔ�댍(sh��)�(y��n)Ӌ(j��)��C(j��)����Ҫ�Ĕ�(sh��)��(j��)���@ʾ�\(y��n)�Д�(sh��)��(j��)���Y(ji��)���c��B(t��i)��

4�� ��(du��)��(sh��)��߉������ϵ�y(t��ng)��(sh��)�(y��n)������Ӌ(j��)��C(j��)�M��ԭ���c�wϵ�Y(ji��)��(g��u)������(sh��)�(y��n)���r(sh��)����debug���x�����A�ˆΣ��Ɍ�(du��)CPU/IP Core��FPGA�Č��ÿ��g���O(sh��)Ӌ(j��)�ļĴ����M(j��n)����ݔ�딵(sh��)��(j��)�ͅ���(sh��)�O(sh��)���Լ��x��Ŀ��(bi��o)ݔ����Ϣ��

4���h(yu��n)���O(sh��)Ӌ(j��)

1�� �����߿���ͨ�^(gu��)�W(w��ng)�j(lu��)��XP�h(yu��n)�������M(j��n)���O(sh��)Ӌ(j��)��(sh��)�(y��n)�������ͬ��Ч��һ�¡�

������(sh��)�(y��n)�n���(xi��ng)Ŀ

A����Ӌ(j��)��C(j��)�M��ԭ�����c��CPU�O(sh��)Ӌ(j��)�c�y(c��)ԇ��

�� CPU�������O(sh��)Ӌ(j��)��(sh��)�(y��n)

1���g�a��

2����(ji��n)��ָ�����Ӳ�������ƣ�

3��16λ�\(y��n)����

4�����A������FPGA��(n��i)SRAM��

5��FIFO���M(j��n)�ȳ��惦(ch��)��

6��8λ�ۼ������p�˿�8×4�ۼ���

7��16λ�λ����λ߉

8��8��(j��)Ƕ�ї�

9������Ӌ(j��)��(sh��)��

10���r(sh��)��߉

11��3�B(t��i)������

�� CPU�O(sh��)Ӌ(j��)��(sh��)�(y��n)

1���Զ��x8λָ��ϵ�y(t��ng)CPU��ָ����ʽ��RISC��CISC��MISC��

2��16λָ��8086/86����CPU��16-40�l��ȫָ���

3��MIPS��12-16�l��32�(ji��n)������CPU��

�� ��(chu��ng)��CPU�O(sh��)Ӌ(j��)(�����ṩ�̎��v�n��(n��i)�ݡ���(sh��)�(y��n)�ļ�PPT���W(xu��)�����I(y��)��(n��i)�ݺ�Ҫ���O(sh��)Ӌ(j��)�����������ęn��

1��LC-3 �Y(ji��)��(g��u)CPU�O(sh��)Ӌ(j��)���̌�(sh��)�(y��n)��

2��LC-3 �Y(ji��)��(g��u)������ˮ�O(sh��)Ӌ(j��)��(sh��)�(y��n)��

B������(sh��)��߉��

Ӌ(j��)��(sh��)������(sh��)�a���g�a�·��ȫ���������l�cϵ�в���4λ��(sh��)��(j��)�h��У�(y��n)����(ji��n)������ͨӍ�ȡ�

C����Ӌ(j��)��C(j��)�wϵ�Y(ji��)��(g��u)��

�� ��CPU���������A�����p�C(j��)��M��S��ͨӍ�����c(di��n)�\(y��n)�������O(sh��)Ӌ(j��)�(y��n)�C�����CPU�����U(ku��)���������·�������D(zhu��n)�Q�����A�����Ϳ��Ʋ��������O(sh��)���w�Y(ji��)��(g��u)�Ȍ�(sh��)�(y��n)��

�� ����O(sh��)��ӿ�߉�O(sh��)Ӌ(j��)��(sh��)�(y��n)����IDE��TFT-LCD��LAN��USB��RS232��LPT�ȡ�

�� ϵ�y(t��ng)BIOS��TOS��(sh��)�(y��n)��

D����Ӳ�������Z(y��)�ԡ��c�����ܶȿɾ���������(y��ng)�á�

VHDL��Verilog��AHD���Z(y��)�Ծ����O(sh��)Ӌ(j��)�������c���d�(y��n)�C��(sh��)�(y��n)��

E����������_(k��i)�l(f��)Ӳ��߉��IP Core�O(sh��)Ӌ(j��)��USB�O(sh��)���_(k��i)�l(f��)�����(y��n)�C����Ӗ(x��n)ϵ�y(t��ng)

���Ќ�(sh��)�(y��n)?z��i)��?bi��o)���O(sh��)Ӌ(j��)��ʹ��Ӳ�������Z(y��)��Verilog HDL����ϵ�y(t��ng)�ɾ�������FPGA/CPLD��(sh��)�F(xi��n)����(sh��)�(y��n)�ЌW(xu��)������Ҫ���κξ����������O(sh��)Ӌ(j��)�c�(y��n)�C�{(di��o)ԇ��

��(sh��)�(y��n)�^(gu��)�̣�Ŀ��(bi��o)��Verilog HDL߉���� → ���gͨ�^(gu��) → ߉ģ�M���棨�ֹ���ģ�壩�(y��n)�C → �ڌ�(sh��)�(y��n)ƽ�_(t��i)�y(c��)ԇ���dĿ��(bi��o)߉�͜y(c��)ԇ����(sh��)��(j��)�y(c��)ԇ�(y��n)�C��

��(du��)FPGAD/CPLD�������d�ṩ플��{(di��o)��Ŀ��(bi��o)��Ԕ�M����ģ������_�����ļ������Ñ����O(sh��)Ӌ(j��)���ṩ�O��ķ��㡣

�����CPU�O(sh��)Ӌ(j��)���wϵ�Y(ji��)��(g��u)��(sh��)�(y��n)���������߀����C�Z(y��)�Ծ�����ָ�����C(j��)���R�������(j��)���g���O(sh��)Ӌ(j��)���O(ji��n)�س���BIOS��Tos����ϵ�y(t��ng)�O(sh��)Ӌ(j��)�����c�������P(gu��n)�n�̵Č�(sh��)�(y��n)����M(j��n)�У���

FPGA�O(sh��)Ӌ(j��)�c����ʹ��Altera��MAX+PlusII10.2��QuartusII4.1-7.2ϵ�y(t��ng)��

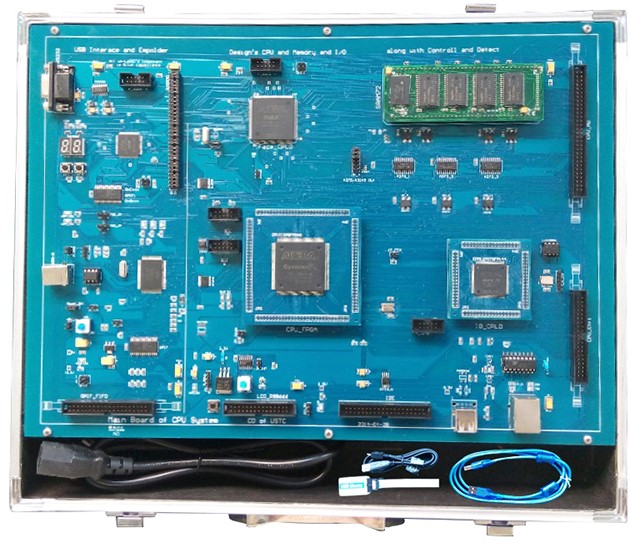

����1. Ӌ(j��)��C(j��)Ӳ��ƽ�_(t��i)������̎��������(n��i)�桢Ӳ�P���@�����W(w��ng)���Ⱥ��ĽM�������ژ�(g��u)���͜y(c��)ԇӋ(j��)��C(j��)ϵ�y(t��ng)��

����2. �Դϵ�y(t��ng)���ṩ��(w��n)�����Դ����(y��ng)���Еr(sh��)߀�����Դ�O(ji��n)�غͱ��o(h��)���ܡ�

����3. ݔ��/ݔ���ӿڣ���USB�����ڡ����ڡ���̫�W(w��ng)�ӿڵȣ������B���ⲿ�O(sh��)��;W(w��ng)�j(lu��)��

����4. �@ʾ�����I�P�����ڲ����ͱO(ji��n)��Ӌ(j��)��C(j��)ϵ�y(t��ng)���\(y��n)�Р�B(t��i)��

����5. ��(sh��)�(y��n)ָ��(d��o)����ܛ�������ܰ�����(sh��)�(y��n)�փ�(c��)���̌W(xu��)ܛ����̓�M��(sh��)�(y��n)�ҵ��YԴ�������Ñ�W(xu��)��(x��)�͌�(sh��)�`��

����Ӌ(j��)��C(j��)�O(sh��)Ӌ(j��)�C�ϼ���ԇ�(y��n)����Ӌ(j��)��C(j��)�ƌW(xu��)�ͼ��g(sh��)�������Ϣ���̵����P(gu��n)���I(y��)�Ľ̌W(xu��)����Ӗ(x��n)�зdz����á�ͨ�^(gu��)ʹ���@�N�O(sh��)�䣬�W(xu��)�������ڌ�(sh��)�`�ЌW(xu��)��(x��)Ӌ(j��)��C(j��)Ӳ����ܛ�����O(sh��)Ӌ(j��)������S�o(h��)�ȼ��ܣ��錢��(l��i)�Ĺ����ṩ���F�Č�(sh��)�`��(j��ng)�(y��n)��

Ӌ(j��)��C(j��)�O(sh��)Ӌ(j��)�C�ϼ���ԇ�(y��n)��

��

һ����(sh��)�(y��n)ƽ�_(t��i)�ܘ�(g��u)�c���c(di��n)

1����ȫ����FPGA/CPLD��ģ�K�ܘ�(g��u)���Y(ji��)��(g��u)֧��USB��GPIF���ق��ͣ��M�����£�

1��USB�O(sh��)���_(k��i)�l(f��)�c�ӿ�ģ�K������USB��������CY7C68013(��8051��(n��i)��)������EEPROM 24LC01B ��SRAM HY62WT081E��EPM3064ATC100����(sh��)��(j��)�����_(k��i)�P(gu��n) SN74CB3Q3245���i���� 74VHC373������USB�ӿڡ�

2��ƽ�_(t��i)�ӿڿ�����CPLDģ�K������EPM3512AQC208��оƬ�����l��DS1080L��JTAG���d�ӿڵȡ�

3��CPU��IP Core��FPGAģ�K��������������EP1C12Q240C8������оƬEPCS4��JTAG���d�ӿڵȡ�

4������ģ�K4MB SRAM����8Ƭ512K SRAM 62V8400A �M�ɣ�1MB Flash��BIOS��TOS����AM29LA800BT�M�ɡ�

5������ӿ��_(k��i)�l(f��)��CPLDģ�K����EPM1270T144C4��JTAG���d�ӿڵȡ�

6��CPU-BUS�U(ku��)��ģ�K����USB�p������MAX3346E��SRAM HY62WT081E

7����̫�W(w��ng)�ӿ�ģ�K����6PT8515������(q��)��(d��ng)��DS90LV011AH�Ͳ�ֽ�����DS90LV012AH��

8������ͨ�Žӿڣ���MAX232�ƽ�D(zhu��n)�Q����RS232-9�ӿڡ�

9��GPIF�ӿڣ���SRAM HY62WT081E��IDC-40�ӿڡ�

10�����O(sh��)Ӌ(j��)CPU�ⲿ�ӿڣ���TFT-LCD�@ʾ�ӿڡ�IDEӲ�P�ӿڡ�LAN�ӿڵȡ�

2���Y(ji��)��(g��u)�`����ڔU(ku��)�䣬�m�˸��N��ͬ�Y(ji��)��(g��u)CPU��Ŀ��(bi��o)�O(sh��)Ӌ(j��)

1����ȫ����FPGA/CPLD�ı���ʹ��Y(ji��)��(g��u)�`��

2������CPU/IP Core��FPGA��30�f(w��n)�T��������ӿڵ�CPLDʹ�ñ����D(zhu��n)�壬������Q�;S�o(h��)��

3����CPU��FPGA�O(sh��)Ӌ(j��)���ஔ(d��ng)?sh��)Ă�����?h��o)�������^�����_�B�ӡ��ṩ플��{(di��o)��Ŀ��(bi��o)��Ԕ�M����ģ������_�����ļ���

4���ӿڿ�����CPLD���f(w��n)�T��ģ�K߉�����_(k��i)�ţ����ķ��㡢�f(shu��)��Ԕ�M��

3�����ƺ�(ji��n)�Σ��������㣬���ܻ��Ŀ��ƺ͙z�y(c��)����

1��������λ���C(j��)�ı�ϵ�y(t��ng)�{(di��o)ԇdebug��WIN2K/XP��ܛ������(du��)CPU����M�ɵČ�(sh��)�(y��n)Ӌ(j��)��C(j��)�����І���ͣ��������d�cУ�(y��n)��

2���چβ�����ָ�����c(di��n)�\(y��n)�Еr(sh��)����CPU�ĸ�ۙ����߉����£�debug���Ԅ�(d��ng)��ۙ�����@ʾCPU��(n��i)���Ĵ�������������B(t��i)����Ϣ���ɼ��r(sh��)�l(f��)�F(xi��n)�e(cu��)�`���Ñ�����CPU�ĸ�ۙ����߉��Լ��x����Ҫ������Ϣ��

3��Ŀ��(bi��o)CPU����ʹ��PC�C(j��)�ĸ��N�ⲿ�O(sh��)�䣬���B�m(x��)�\(y��n)�Еr(sh��)��ͨ�^(gu��)�p�C(j��)�����C(j��)�cĿ��(bi��o)CPU��ͨӍ���Д�IO��ʽ����ݔ�댍(sh��)�(y��n)Ӌ(j��)��C(j��)����Ҫ�Ĕ�(sh��)��(j��)���@ʾ�\(y��n)�Д�(sh��)��(j��)���Y(ji��)���c��B(t��i)��

4�� ��(du��)��(sh��)��߉������ϵ�y(t��ng)��(sh��)�(y��n)������Ӌ(j��)��C(j��)�M��ԭ���c�wϵ�Y(ji��)��(g��u)������(sh��)�(y��n)���r(sh��)����debug���x�����A�ˆΣ��Ɍ�(du��)CPU/IP Core��FPGA�Č��ÿ��g���O(sh��)Ӌ(j��)�ļĴ����M(j��n)����ݔ�딵(sh��)��(j��)�ͅ���(sh��)�O(sh��)���Լ��x��Ŀ��(bi��o)ݔ����Ϣ��

4���h(yu��n)���O(sh��)Ӌ(j��)

1�� �����߿���ͨ�^(gu��)�W(w��ng)�j(lu��)��XP�h(yu��n)�������M(j��n)���O(sh��)Ӌ(j��)��(sh��)�(y��n)�������ͬ��Ч��һ�¡�

������(sh��)�(y��n)�n���(xi��ng)Ŀ

A����Ӌ(j��)��C(j��)�M��ԭ�����c��CPU�O(sh��)Ӌ(j��)�c�y(c��)ԇ��

�� CPU�������O(sh��)Ӌ(j��)��(sh��)�(y��n)

1���g�a��

2����(ji��n)��ָ�����Ӳ�������ƣ�

3��16λ�\(y��n)����

4�����A������FPGA��(n��i)SRAM��

5��FIFO���M(j��n)�ȳ��惦(ch��)��

6��8λ�ۼ������p�˿�8×4�ۼ���

7��16λ�λ����λ߉

8��8��(j��)Ƕ�ї�

9������Ӌ(j��)��(sh��)��

10���r(sh��)��߉

11��3�B(t��i)������

�� CPU�O(sh��)Ӌ(j��)��(sh��)�(y��n)

1���Զ��x8λָ��ϵ�y(t��ng)CPU��ָ����ʽ��RISC��CISC��MISC��

2��16λָ��8086/86����CPU��16-40�l��ȫָ���

3��MIPS��12-16�l��32�(ji��n)������CPU��

�� ��(chu��ng)��CPU�O(sh��)Ӌ(j��)(�����ṩ�̎��v�n��(n��i)�ݡ���(sh��)�(y��n)�ļ�PPT���W(xu��)�����I(y��)��(n��i)�ݺ�Ҫ���O(sh��)Ӌ(j��)�����������ęn��

1��LC-3 �Y(ji��)��(g��u)CPU�O(sh��)Ӌ(j��)���̌�(sh��)�(y��n)��

2��LC-3 �Y(ji��)��(g��u)������ˮ�O(sh��)Ӌ(j��)��(sh��)�(y��n)��

B������(sh��)��߉��

Ӌ(j��)��(sh��)������(sh��)�a���g�a�·��ȫ���������l�cϵ�в���4λ��(sh��)��(j��)�h��У�(y��n)����(ji��n)������ͨӍ�ȡ�

C����Ӌ(j��)��C(j��)�wϵ�Y(ji��)��(g��u)��

�� ��CPU���������A�����p�C(j��)��M��S��ͨӍ�����c(di��n)�\(y��n)�������O(sh��)Ӌ(j��)�(y��n)�C�����CPU�����U(ku��)���������·�������D(zhu��n)�Q�����A�����Ϳ��Ʋ��������O(sh��)���w�Y(ji��)��(g��u)�Ȍ�(sh��)�(y��n)��

�� ����O(sh��)��ӿ�߉�O(sh��)Ӌ(j��)��(sh��)�(y��n)����IDE��TFT-LCD��LAN��USB��RS232��LPT�ȡ�

�� ϵ�y(t��ng)BIOS��TOS��(sh��)�(y��n)��

D����Ӳ�������Z(y��)�ԡ��c�����ܶȿɾ���������(y��ng)�á�

VHDL��Verilog��AHD���Z(y��)�Ծ����O(sh��)Ӌ(j��)�������c���d�(y��n)�C��(sh��)�(y��n)��

E����������_(k��i)�l(f��)Ӳ��߉��IP Core�O(sh��)Ӌ(j��)��USB�O(sh��)���_(k��i)�l(f��)�����(y��n)�C����Ӗ(x��n)ϵ�y(t��ng)

���Ќ�(sh��)�(y��n)?z��i)��?bi��o)���O(sh��)Ӌ(j��)��ʹ��Ӳ�������Z(y��)��Verilog HDL����ϵ�y(t��ng)�ɾ�������FPGA/CPLD��(sh��)�F(xi��n)����(sh��)�(y��n)�ЌW(xu��)������Ҫ���κξ����������O(sh��)Ӌ(j��)�c�(y��n)�C�{(di��o)ԇ��

��(sh��)�(y��n)�^(gu��)�̣�Ŀ��(bi��o)��Verilog HDL߉���� → ���gͨ�^(gu��) → ߉ģ�M���棨�ֹ���ģ�壩�(y��n)�C → �ڌ�(sh��)�(y��n)ƽ�_(t��i)�y(c��)ԇ���dĿ��(bi��o)߉�͜y(c��)ԇ����(sh��)��(j��)�y(c��)ԇ�(y��n)�C��

��(du��)FPGAD/CPLD�������d�ṩ플��{(di��o)��Ŀ��(bi��o)��Ԕ�M����ģ������_�����ļ������Ñ����O(sh��)Ӌ(j��)���ṩ�O��ķ��㡣

�����CPU�O(sh��)Ӌ(j��)���wϵ�Y(ji��)��(g��u)��(sh��)�(y��n)���������߀����C�Z(y��)�Ծ�����ָ�����C(j��)���R�������(j��)���g���O(sh��)Ӌ(j��)���O(ji��n)�س���BIOS��Tos����ϵ�y(t��ng)�O(sh��)Ӌ(j��)�����c�������P(gu��n)�n�̵Č�(sh��)�(y��n)����M(j��n)�У���

FPGA�O(sh��)Ӌ(j��)�c����ʹ��Altera��MAX+PlusII10.2��QuartusII4.1-7.2ϵ�y(t��ng)��